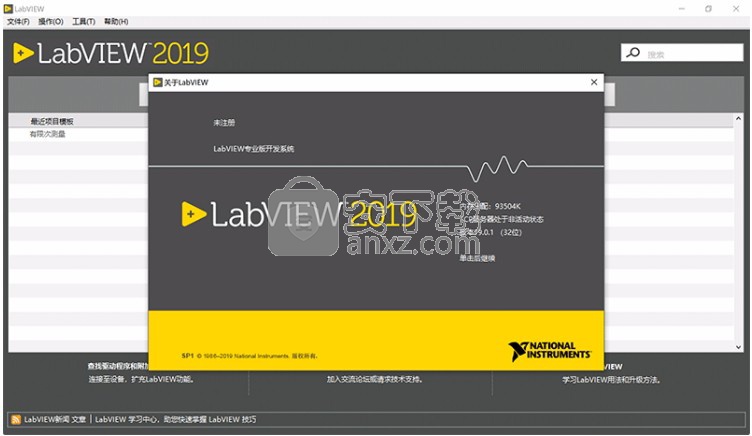

NI LabView 2019 SP1 32位中文

附安装教程大小:1710 MB 更新:2023/03/24

类别:编程工具系统:WinXP, Win7, Win8, Win10, WinAll

分类分类

大小:1710 MB 更新:2023/03/24

类别:编程工具系统:WinXP, Win7, Win8, Win10, WinAll

NI LabView 2019 SP1 32位中文版是LabView 2019系列软件的新版本;此版本为用户提供非常多的开发中心,同时还内置很多功能模块,可以有效的帮助工程师在短时间之内完成开发;程序为用户提供了可支持各种Linux版本的模块,它们同样也适用于嵌入式应用,从而解决了院校和工业界Linux使用者的不同需求;新版本还构建实时Linux嵌入式系统,NI开发了具有内置工业级实时性能的全新Linux操作系统NI Linux Real-Time;该操作系统专为嵌入式系统而开发,它不仅可提供实时性能,而且具有桌面操作系统的方便性和易用性;需要的用户可以下载体验

1、无缝集成硬件,快速将ni硬件和第三方设备集成到一个开发环境中,以满足应用需求。

2、集成分析函数和ip,节省时间,利用内置函数或调用现成ip进行分析和控制,更快速获取有用信息。

3、将数据可视化,便于管理系统,使用拖放式方法开发用户界面,查看数据、制定决策和管理已部署的系统。

4、设计智能机器或工业设备,借助labview2019,更快速地构建工业设备和智能机器。NI的嵌入式设计平台结合了完整的软件堆栈、紧密集成且可定制的硬件以及充满活力的用户和IP生态系统。

5、工科课程教学,借助labview2019,您可以在教室或实验室中基于真实系统进行授课,帮助学生更快速进行探索、更快速构建解决方案以及提高成功概率。

1、使用经验证且可定制的硬件,快速进行设计迭代

LabVIEW可与NI现成即用且可定制的硬件紧密集成,无需使用中间件。 统一的开发环境为NI FPGA和NI Linux Real-Time OS提供经验证的完整软件堆栈,帮助您在整个设计周期中快速进行迭代。

2、使用高级控制和分析程序,缩短开发时间

LabVIEW包含了1,000多个高级控制和分析库以及针对智能机器和工业系统的专用函数。您可以复用使用The MathWorks, Inc. MATLAB、Eclipse和CODESYS 软件或VHDL、C/C ++/C#和Python等编程语言创建的代码,从而专注于执行,而不是集成。

3、无缝连接第三方设备和监控系统

NI可定制的现成嵌入式硬件和LabVIEW可以充当网关,通过各种可支持的工业通信协议(如EtherCAT、以太网/IP、Modbus、OPC UA)集成各种现有设备、仪器和基础设施。

4、快速创建基于web的用户界面

LabVIEW NXG Web模块通过拖放式工程UI设计、直观的通信机制和安全的托管选项,简化了基于Web的用户界面的设计和部署,可让用户远程查看过程数据。

5、简化分布式系统的部署和复制

LabVIEW提供了直观的API和复制工具,可对连接的设备、软件部署和系统诊断进行大规模协调,在开发环境中直接简化了部署和系统管理任务。

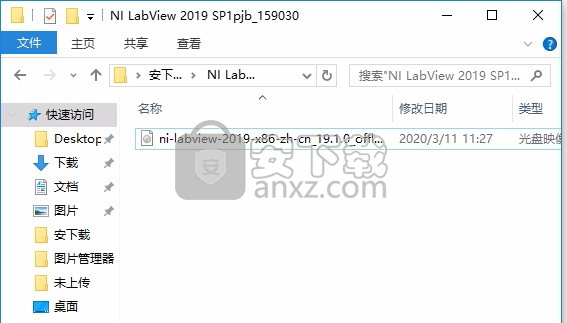

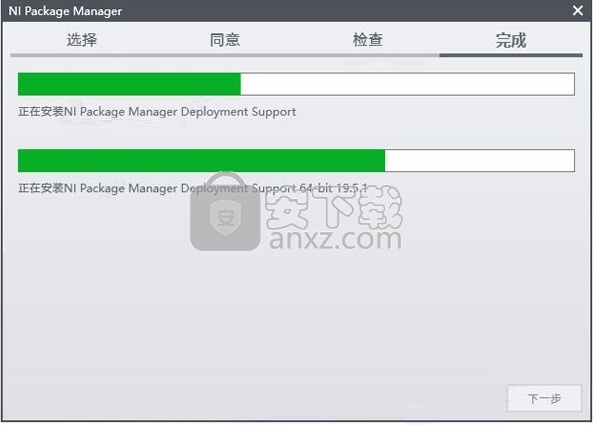

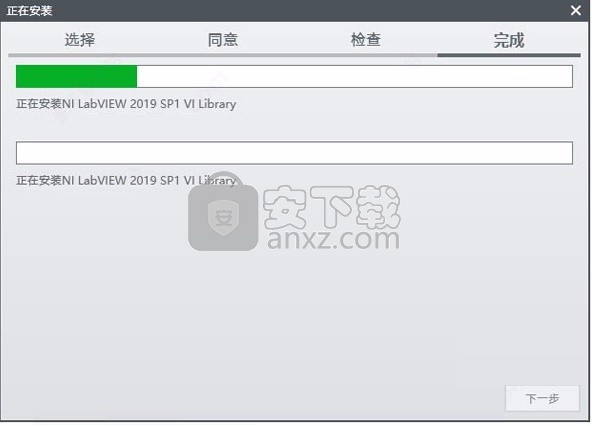

1、用户可以点击本网站提供的下载路径下载得到对应的程序安装包

2、只需要使用解压功能将压缩包打开,双击主程序即可进行安装,弹出程序安装界面

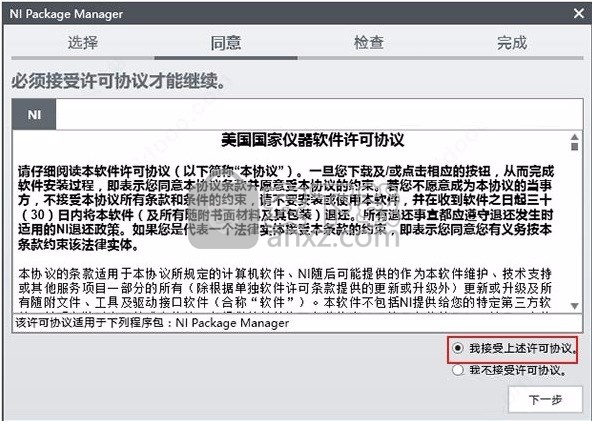

3、同意上述协议条款,然后继续安装应用程序,点击同意按钮即可

4、弹出以下界面,用户可以直接使用鼠标点击下一步按钮,可以根据您的需要不同的组件进行安装

5、根据提示点击安装,弹出程序安装完成界面,点击完成按钮即可

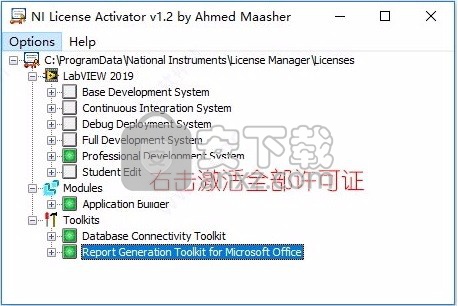

1、安装完毕打开文件夹,打开NI License Activator 1.2.exe注册机,将所有白色的小方块激活,点击右键,点击activate;全部变为绿色以后你的主程序就可以正常使用,从而实现

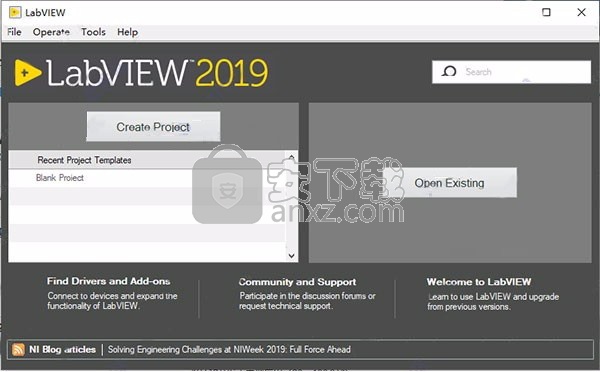

2、找到您需要使用的labview2019模块打开就可以使用

通过将第三方IP 集成到NI LabVIEW软件,您能使用许多的针对Xilinx现场可编程门整列(Field-programmable gate arrays, FPGA)进行优化的算法,在实现高性能的同时提高代码重用度。LabVIEW FPGA模块提供两种方法用来实现外部代码的导入:组件级IP(Component-Level Intellectual Property, CLIP)节点和IP集成节点。本白皮书将讨论这两种方法。

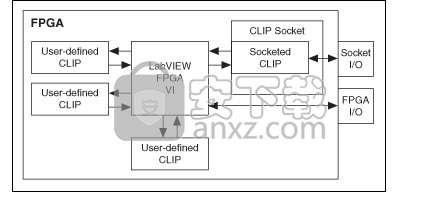

CLIP节点介绍

CLIP节点是一种用于将已有的FPGA IP导入LabVIEW FPGA硬件的同时通过LabVIEW FPGA程序框图与它进行通讯的框架。一旦导入成功,相对于LabVIEW FPGA,IP可以独立地、并行地运行。IP既能以原始VHDL的形式也能以诸如电子设计交换格式(Electronic design interchange format, EDIF)网表等中间文件的形式存在。这一功能要求使用者具有一定数字电路设计经验和VHDL的基本知识,因为所导入的IP通常是一种底层的硬件描述语言(Hardware description language, HDL)。

用户定义的CLIP—导入VHDL代码,直接与FPGA VI进行通讯。

套接字CLIP—导入VHDL代码,直接和不与LabVIEW FPGA模块关联的一个FPGA VI以及FPGA引脚进行通信。一些FPGA目标在FPGA中定义了一个您可以插入套接字CLIP的固定式CLIP套接字。

图1. 在由使用者定义的CLIP节点中导入VHDL代码可以与一个FPGA VI进行通讯;反之,一个套接字CLIP节点允许IP同时连接到FPGA VI和可用FPGA引脚。

. 在FPGA应用中使用CLIP

以下步骤概述了在一个FPGA 应用中使用CLIP的过程:

创建或者获取IP。

在FPGA目标属性中声明CLIP以及定义IP接口。

将CLIP添加到项目中。

在一个FPGA VI中使用CLIP。

创建或者获取IP

要将CLIP添加到一个FPGA目标中,您必须提供VHDL代码形式的IP以编译成FPGA对象。您能使用以下方式提供VHDL代码::

创建VHDL代码。

通过其它的硬件描述语言(HDL)创建您自己的可兼容IP核心,例如通过Xilinx CORE Generator利用Verilog进行创建。

从Xilinx或合作伙伴那购买IP核心。

注意:在LabVIEW FPGA的CORE Generator IP选板中有超过50种Xilinx IP模块,无需使用CLIP或IP集成节点导入IP模块您就能将其集成到您的LabVIEW FPGA VI的数据流中。

在使用CLIP节点时,需要特别注意的是LabVIEW FPGA所支持的数据类型以及如何将它们转换为VHDL数据类型。如果您的IP使用的逻辑向量并不不是表一中所列的数据类型之一,您必须编写一个VHDL外层程序来对标准LabVIEW类型进行扩展、缩短或者分解,从而符合IP的数据宽度。

在FPGA目标的属性中声明CLIP以及定义IP接口

注意:以下示例使用附件中的simple_and.vhd文件演示如何将IP导入到一个由用户定义的CLIP节点。

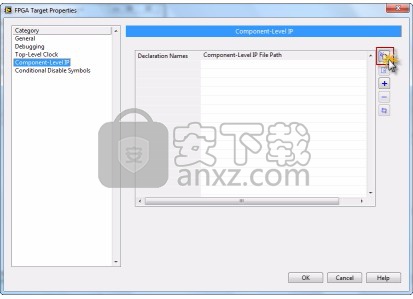

为了将IP的输入和输出映射到LabVIEW 的I/O,使用FPGA目标属性向导创建一个定义了IP必要属性的XML文件。按照以下步骤完成这个任务。

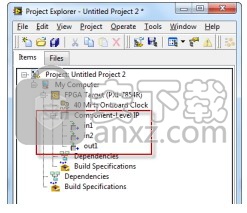

创建一个带有FPGA硬件新LabVIEW项目。右键点击FPGA目标,并选择属性。属性对话框有一段标有“组件级IP(Component-Level IP)”的部分。点击创建文件按钮创建XML文件。

图2. 点击“Create File”开始定义XML声明文档。

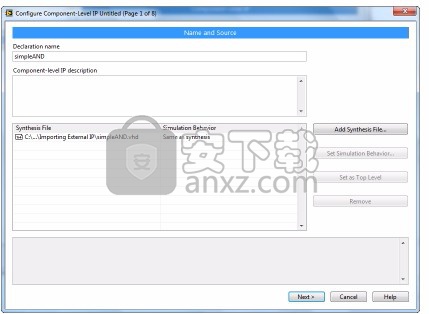

点击Add Synthesis File…按钮,并浏览代表顶层组件IP(即simple_and.vhd )的VHDL文档.再点击Next>

图3. 添加了您的IP的综合文件后,点击Next>。

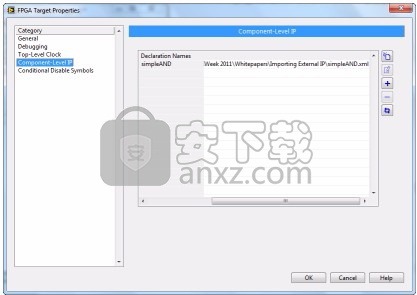

配置向导的余下部分用来安装XML声明文档。本例中,点击Next>按钮默认安装向导的余下部分,验证输入文件的语法,再点击剩下的Next>按钮。

配置向导的余下部分用来安装XML声明文档。本例中,点击Next>按钮默认安装向导的余下部分,验证输入文件的语法,再点击剩下的Next>按钮。

图4. 配置向导中生成的XML声明文件必须为导入的IP模块而列出。

一旦您完成了CLIP配置向导,CLIP声明名称(在XML文档中已定义)将出现在文件的路径旁。在本对话框中,您能够为需要导入的所有不同IP模块声明多个CLIP节点。

将一个CLIP项添加到一个LabVIEW项目中

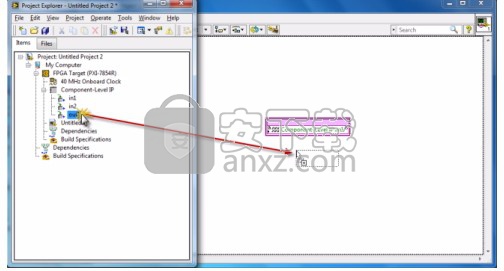

在FPGA中声明CLIP实际上并没有将它添加到项目中去,因为你能够在同一个FPGA上完成一个CLIP的多个实例。在下一步中,你将创建一个先前已经被声明的simpleAND CLIP项的实例。

右键点击FPGA目标,并选择New Component-Level IP。在CLIP对话框中会出现选择所需的 CLIP,给这个实例一个唯一的标识名,以及通过“Clock”信号类型,选择时钟连接到CLIP中的任意线路。在本例中,后面两个选项默认不选。

图5. 本对话框显示当你将一个CLIP的实例添加到项目中后,选择CLIP,定义一个名称,同时配置时钟。

一旦您点击本对话框中的OK按钮,本CLIP和出现在项目中的所有与之相关的输入和输出都被标有该实例的名称。

图6. 添加CLIP后的项目后,显示IP的所有I/O节点。

在CLIP和一个FPGA VI之间传递数据

此时,你已经准备好在CLIP和FPGA VI间进行通讯。你要做的只是从项目中将所需的I/O节点拖放到FPGA框图中。您的IP必须具有如何使用IP的文档。比如,许多IP模块使用一些类型的握手线用于数据的输入和输出,它们通常被标记为“data valid ”或者 “enable”。使用LabVIEW的数据类型,在正确的时间发送正确的数值,即可运行IP。您可将CLIP I/O放置在一个单周期定时循环(Single-cycle Timed Loop, SCTL)内部或者外部,但是请记住,在一个SCTL内部,你可能需要考虑时钟域交叉以及使用同步寄存器。

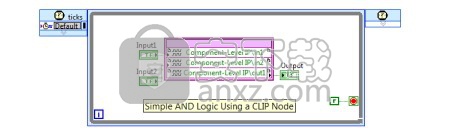

图7. 为了在LabVIEW FPGA中与CLIP进行通讯,将项目窗口中IP输入和输出拖放到FPGA VI的框图中。

图8. 使用CLIP, 整个的LabVIEW FPGA方框图与所导入的IP进行通讯。

IP集成节点介绍

注意:这个IP集成节点范例将导入附件中的demo_adder.vhd IP模块。

创建一个带有FPGA目标的LabVIEW项目,同时在FPGA目标下添加一个新的VI

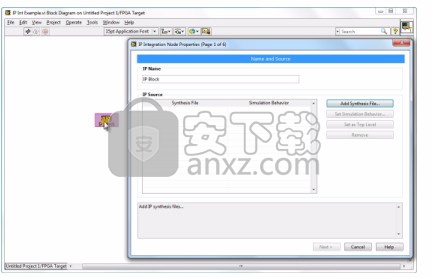

在新建的VI的程序框图中,从编程选板中拖放一个IP Integration Node,保存FPGA VI,再双击节点打开配置向导对话框。

图9. 双击IP集成节点,使用属性配置向导开始导入步骤。

点击Add Synthesis File,在弹出的窗口中选择demo_adder.vhd文档。

返回到配置向导对话框,两次点击Next>选择默认选项。

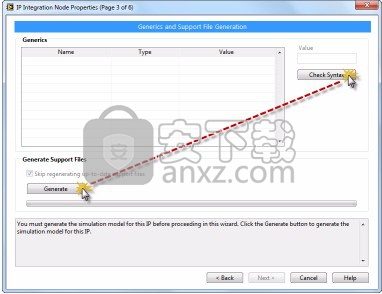

在文件生成步骤,首先确认导入的VHDL文档的语法,然后通过点击如下所示的各个按钮生成支持文件。

图10. 配置向导使帮助您在生成必须的LabVIEW支持文件之前检查您的VHDL IP的语法。

一旦IP生成成功,在后续的三步中选择Next>保持默认选项。

在配置向导的最后一步中,你能够为不同的终端选择数据类型。对这一IP模块,默认的定点数据类型即可满足要求。点击Finish按钮完成生成。

IP集成节点现已配置成功,同时您可以将其集成进您的其它的LabVIEW FPGA应用中。

图11. IP集成节点及其集成的IP

LIP和IP集成节点的区别

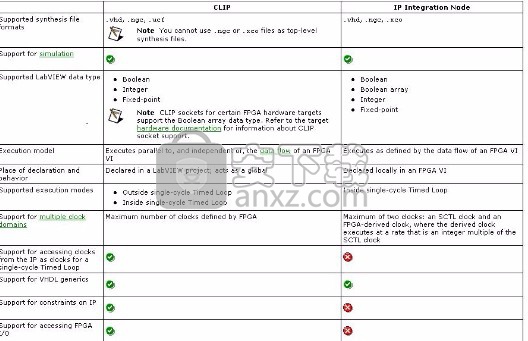

CLIP 和 IP集成节点是将外部IP导入LabVIEW FPGA的两种方式,你必须根据以下的标准在二者之间进行选择。CLIP节点能够与您在LabVIEW FPGA中开发的IP 独立地并行运行。此外,CLIP能够直接与FPGA时钟和I/O引脚进行联接。与此相反,IP集成节点则被植入LabVIEW FPGA程序框图中,并按照LabVIEW VI数据流所定义的方式执行。作为LabVIEW 数据流的一部分,使用周期精准的仿真工具,IP集成节点使您可以验证整体的应用行为和时序。

Embarcadero RAD Studio(多功能应用程序开发工具) 编程工具177.22 MB12

详情猿编程客户端 编程工具173.32 MB4.16.0

详情猿编程 编程工具173.32 MB4.16.0

详情VSCodium(VScode二进制版本) 编程工具76.23 MBv1.57.1

详情aardio(桌面软件快速开发) 编程工具9.72 MBv35.69.2

详情一鹤快手(AAuto Studio) 编程工具9.72 MBv35.69.2

详情ILSpy(.Net反编译) 编程工具3.97 MBv8.0.0.7339 绿色

详情文本编辑器 Notepad++ 编程工具7.81 MBv8.1.3 官方中文版

详情核桃编程 编程工具272.43 MBv2.1.120.0 官方版

详情delphi2007完整 编程工具1198 MB附安装教程

详情SAPIEN PrimalScript2015 编程工具78.02 MB附带安装教程

详情Alchemy Catalyst可视化汉化工具 编程工具81.00 MBv13.1.240

详情Professional Tag Editor(通用标签编辑器) 编程工具25.6 MBv1.0.6.8

详情Coffeecup HTML Editor(html网页编辑器) 编程工具68.98 MBv15.4 特别版

详情JCreator Pro 编程工具9.65 MBv5.0.1 汉化

详情WebStorm 12中文 编程工具209.88 MB附带安装教程

详情MSWLogo(多功能项目开发与管理工具) 编程工具2.25 MBv6.5 免费版

详情JetBrains datagrip 2018.2.1中文-datagrip 2018.2.1 编程工具160.88 MB附注册码汉化包

详情易安卓5.0 编程工具202 MBv5.0 附破解补丁

详情keil uvision5 编程工具271.63 MB附带安装教程

详情CIMCO Edit V8中文 编程工具248 MB附安装教程

详情IntelliJ IDEA 2020.1(java集成开发环境) 编程工具643.0 MB附安装教程

详情redis desktop manager2020.1中文 编程工具32.52 MB附带安装教程

详情猿编程 编程工具173.32 MB4.16.0

详情信捷PLC编程工具软件 编程工具14.4 MBv3.5.2 官方版

详情源码编辑器 编程工具201.0 MBv3.4.3 官方版

详情Microsoft Visual C++ 编程工具226.00 MBv6.0 SP6 简体中文版

详情s7 200 smart编程软件 编程工具187 MBv2.2 官方中文版

详情TouchWin编辑工具(信捷触摸屏编程软件) 编程工具55.69 MBv2.D2c 官方版

详情易语言5.8完美 编程工具312 MB5.8.1 破解增强版

详情Scraino(少儿编程软件) 编程工具272.93 MBv0.3.0 官方版

详情vs2008中文 编程工具1495 MB附序列号

详情e盾网络验证源码 编程工具25.77 MBV45 官方版

详情codeblocks 编程工具95.21 MBv13.12 中文完整版(带GNW编译器

详情Android Studio(安卓开发环境) 编程工具983.0 MBv3.5.0.21 汉化版(附安装教程)

详情源码编辑器pc版 编程工具201.0 MBv3.4.3 官方版

详情CH341A编程器 编程工具1.06 MB1.30 绿色中文版

详情layuiAdmin pro(layui后台管理模板系统) 编程工具0.57 MBv1.1.0 单页版

详情海龟编辑器 编程工具71.5 MBv0.8.4 中文版

详情Ardublock中文版(Arduino图形化编程软件) 编程工具2.65 MB附带安装教程

详情文本编辑器 Notepad++ 编程工具7.81 MBv8.1.3 官方中文版

详情富途牛牛 编程工具160.59 MBv11.8.9068 官方版

详情微信开发者工具 编程工具129.37 MBv1.05.2105170 官方版

详情UEStudio v18.0.0.18 简体中文绿色 编程工具19.00 MB

详情十六进制编辑器 WinHex 编程工具2.79 MBv20.2 SR-5

详情代码编辑器 Sublime Text 编程工具54.74 MBv4.0.0.4126

详情RJ TextEd(代码编辑器) 编程工具49.46 MBv15.31

详情核桃编程 编程工具272.43 MBv2.1.120.0 官方版

详情影刀 编程工具306.37 MBv4.9.14

详情Kate(高级文本编辑器) 编程工具56.11 MBv21.12.1.1544

详情